People

- Nawaf Almoosa

- William Song

- He Xiao

- Xinwei Chen

- Karthik Rao

Collaborators

Sponsors

Power and Thermal Management

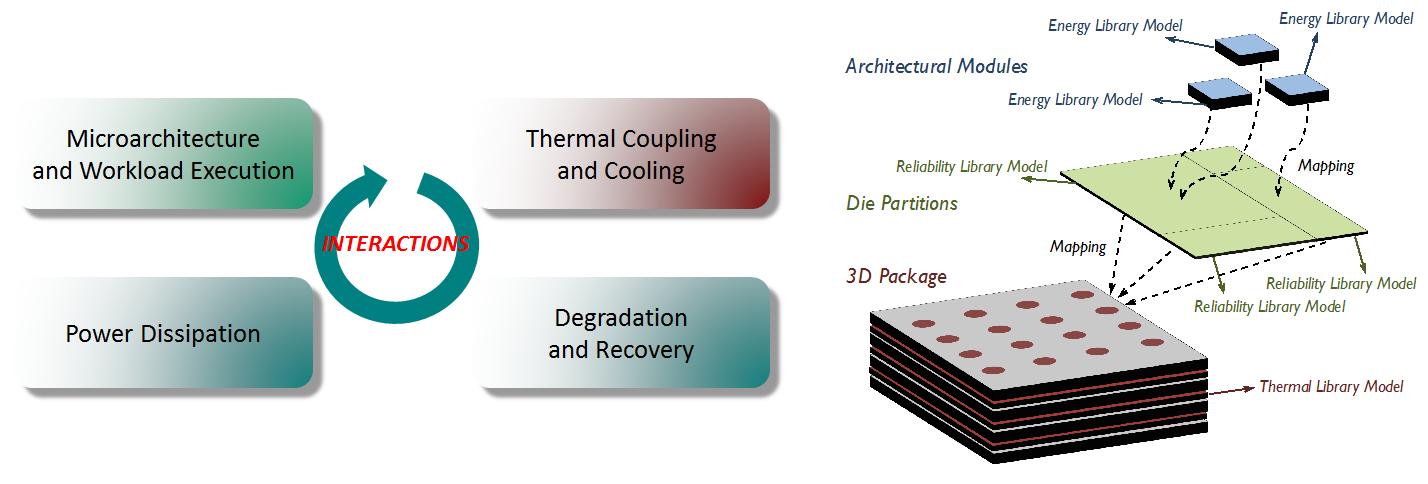

As industry moves to increasingly small feature sizes, performance scaling will become dominated by the physics of the computing environment. There are fundamental trade-offs to be made at the architectural level between performance, energy/power, and reliability. We refer to the body of knowledge addressing the impact of physics on such system level metrics as the processor physics. Relatively few efforts to date have targeted understanding, characterizing, and managing the multi-physics and multi-scale (nanoseconds to milliseconds) transient interactions between delivery, dissipation, and removal (cooling) of energy and their impact on system level performance. This includes traditional issues of power and thermal management as well as reliability management, but more recently the modeling and control of interactions and tradeoffs between them. We are focused on modeling and understanding tradeoffs between energy, performance, and reliability, ii) understanding the impact of fluidic cooling technology, and iii) control-theoretic power and thermal management.

Publications

The papers are provided for personal use and are subject to copyright of the publishers.

- W. Song, S. Mukhopadhyay, and S. Yalamanchili, “Lifetime Reliability and Accelerated Execution,” SRC TECHCON, September 2013. (Best in Session Award)

- M. Cho, K. Z. Ahmed, W. Song, S. Yalamanchili, and Saibal Mukhopadhyay, “Methods and Circuits for Post-Silicon Characterization and Prediction of Transient Thermal Field in Integrated Circuits,” to appear in IEEE Transactions on Components, Packaging and Manufacturing Technology. 2013.

- Sudhakar Yalamanchili. “New Rules: Managing Processor Physics to Sustain Reliable Performance Scaling.” Third Workshop on Energy-Secure System Architectures (ESSA), held in conjunction with ISCA-2013. June 2013. slides

- I. Paul, S. Manne, M. Arora, W. L. Bircher and S. Yalamanchili, “Cooperative Boosting: Needy Versus Greedy Power Management.” IEEE/ACM International Symposium on Computer Architecture (ISCA-2013). June 2013. paper

- S. Yalamanchili. “Architectural Alternatives for Energy Efficient Performance Scaling.” 26th IEEE International Conference on VLSI Design, Special Session on Low Power Computing – Reducing the gap between the Physical and Practical Limits. January 2013. slides

- M. Cho, C. Kersey, M. Gupta, N. Sathe, S. Kumar, S. Yalamanchili, and S. Mukhopadhyay, “Power Multiplexing for Thermal Field Management in Many Core Processors,” IEEE Transactions on Components, Packaging and Manufacturing Technology, vol.3, issue.1. January 2013.

- N. Almoosa, W. J Song, Y Wardi, and S. Yalamanchili, “A Power Capping Controller for Multicore Processors,” IEEE American Control Conference, June 2012.

- W. Song, S. Mukhopadhyay, and S. Yalamanchili, “Reliability Implications of Power and Thermal Constrained Operation of Asymmetric Multicore Processors,” Dark Silicon Workshop, June 2012.

- M. Cho, W. Song, S. Yalamanchili, and S. Mukhopadhyay, “Thermal System Identification (TSI): A Methodology for Post-silicon Characterization and Prediction of the Transient Thermal Field in Multicore Chips,” IEEE Symposium on Thermal Measurement, Modeling, and Management, March 2012.

- S. Chatterjee, M. Rasquinha, S. Yalamanchili, and S. Mukhopadhyay, “A Scalable Design Methodology for Energy Minimization of STTRAM: A Circuit and Architecture Perspective,” IEEE Transactions on VLSI, vol. 19, no. 5, pp. 809-817, May 2011.

- S. Chatterjee, S. Mukhopadhyay, M. Rasquinha, S. Yalamanchili, S. Bhania, A. Paul, “Energy Efficient Circuit-System Co-Design for Spin Torque Transfer Random Access Memory (STTRAM) in Submicron Technologies,” Proceedings of the Second Annual Non-Volatile Memories Workshop, March 2011.

- K. Chae, M. Rasquinha, S. M. Hasan, S. Yalamanchili, and S. Mukhopadhyay, “Statistical Analysis of the Effect of Network on Performance of Many-Core Platform with 3D-Stacked DRAM,” SRC TECHCON, Sept. 2011.

- M. Cho, W. Song, S. Yalamanchili, and S. Mukhopadhyay, “Modeling of the Thermal Field of Many-Core System using Frequency Domain System Identification,” SRC TECHCON, Sept.2011.

- W. J. Song, M. Cho, S. Yalamanchili, S. Mukhopadhyay, and A. F. Rodrigues “Energy Introspector: Simulation Infrastructure for Power, Temperature, and Reliability Modeling in Manycore Processors,” SRC TECHCON, Sept. 2011.

- M. Rasquinha, S. M. Hassan, W. Song, K. Chae, M. Cho, S. Mukhopadhyay, and S. Yalamanchili, “System Impact of 3D Processor-Memory Interconnect: A Limit Study,” SRC TECHCON, Sept. 2011.

- W. Song, S. Mukhopadhyay, and S. Yalamanchili, “Architecture Simulation Framework for 3D ICs,” SRC TECHCON, Sept.2012.

- M. Rasquinha, D. Choudhary, S. Chatterjee, S. Mukhopadhyay, and S. Yalamanchili, “An Energy Efficient Cache Design Using Spin Torque Transfer (STT) RAM,” IEEE/ACM International Symposium on Low Power Electronics and Design, August 2010.

- N. Almoosa, Y. Wardi, and S. Yalamanchili, “Controller Design for Tracking Induced Miss Rate in Cache Memories,” Proceedings of the IEEE International Conference on Control and Automation, June 2010.

- M. Cho, N. Sathe, M. Gupta, S. Kumar, S. Yalamanchili, and S. Mukhopadhyay, “Proactive Power Migration to Reduce Maximum Value and Spatiotemporal Non-uniformity of On-chip Temperature Distribution in Homogeneous Many-Core Processors,” Proceedings of the 26th IEEE Annual Thermal Measurement, Modeling and Management Symposium, 2010

- S. Chatterjee, M. Rasquinha, S. Mukhopadhyay, and S. Yalamanchili, “A Methodology for Robust, Energy Efficient Design of Spin-Torque-Transfer RAM Arrays at Scaled Technologies,” Proceedings of ICCAD, December 2009.